I2C is "Inter-Integrated Circuit"

Interface

SCL : Serial Clock (Output from master)

SDA : Serial DATA (Data In & Out port)

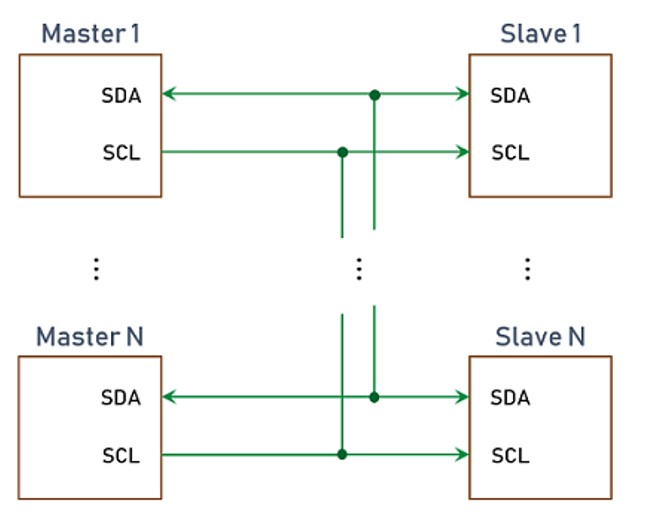

I2C 프로토콜은 하나의 데이터 라인 (SDA)과 하나의 클럭 라인 (SCL)을 이용하는 동기식 (synchronous) 시리얼 통신 방식입니다. 하드웨어 구조는 복잡하지만, 위 그림에서 볼 수 있는 것처럼 서로 다른 모듈간의 wiring 연결이 간단하고, 하나의 Master에서 여러 개의 Slave를 제어할 수 있다는 특징이 있습니다.

Controls the IO expanders, various sensors, EEPROM, ADCs/DACs, and much more. All of which are controlled with only 2 pins from the master.

1개의 마스터와 2개의 line으로 다양한 모듈들을 컨트롤 할 수 있습니다.

Structure

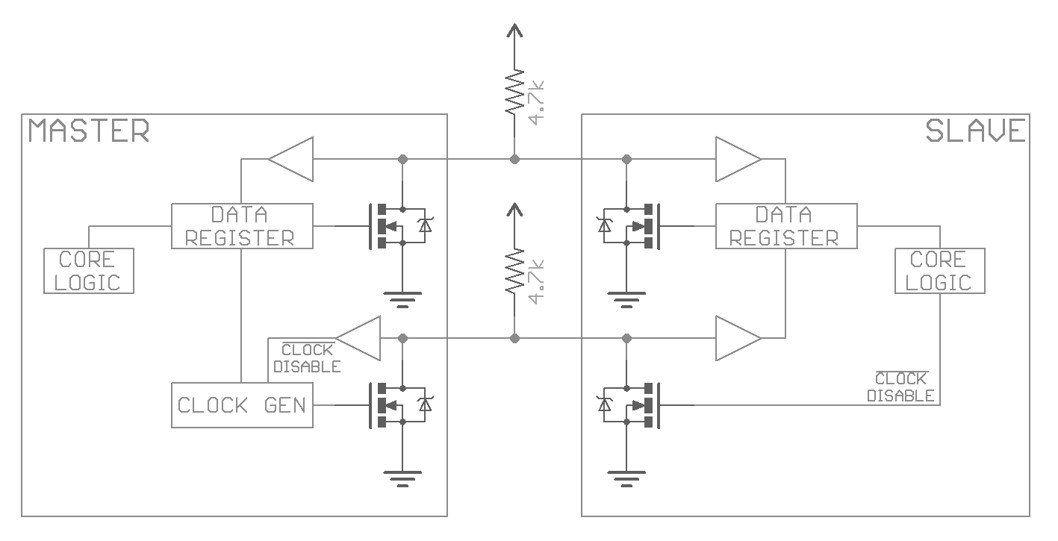

Open-Drain for Bidirectional Communication

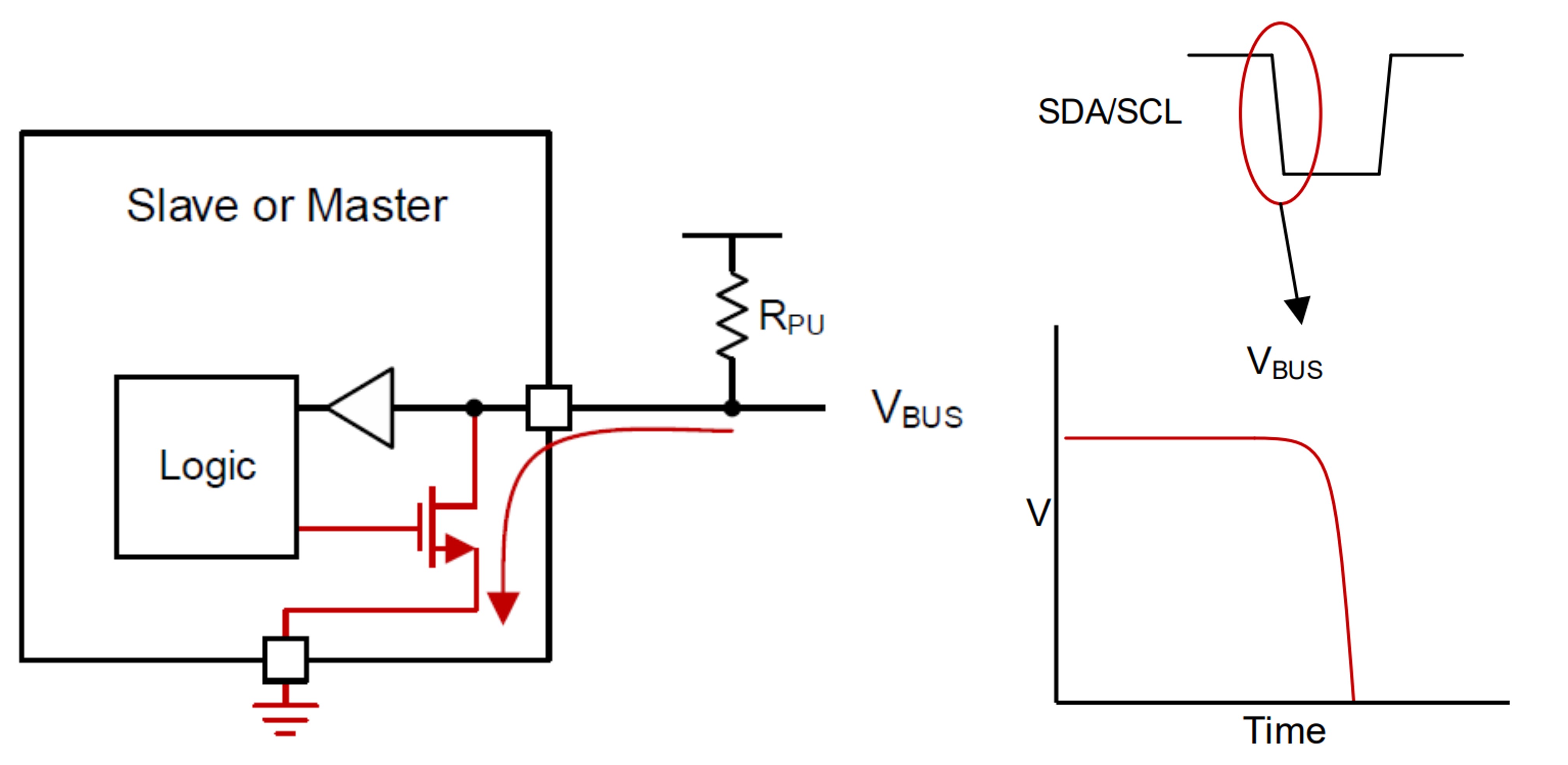

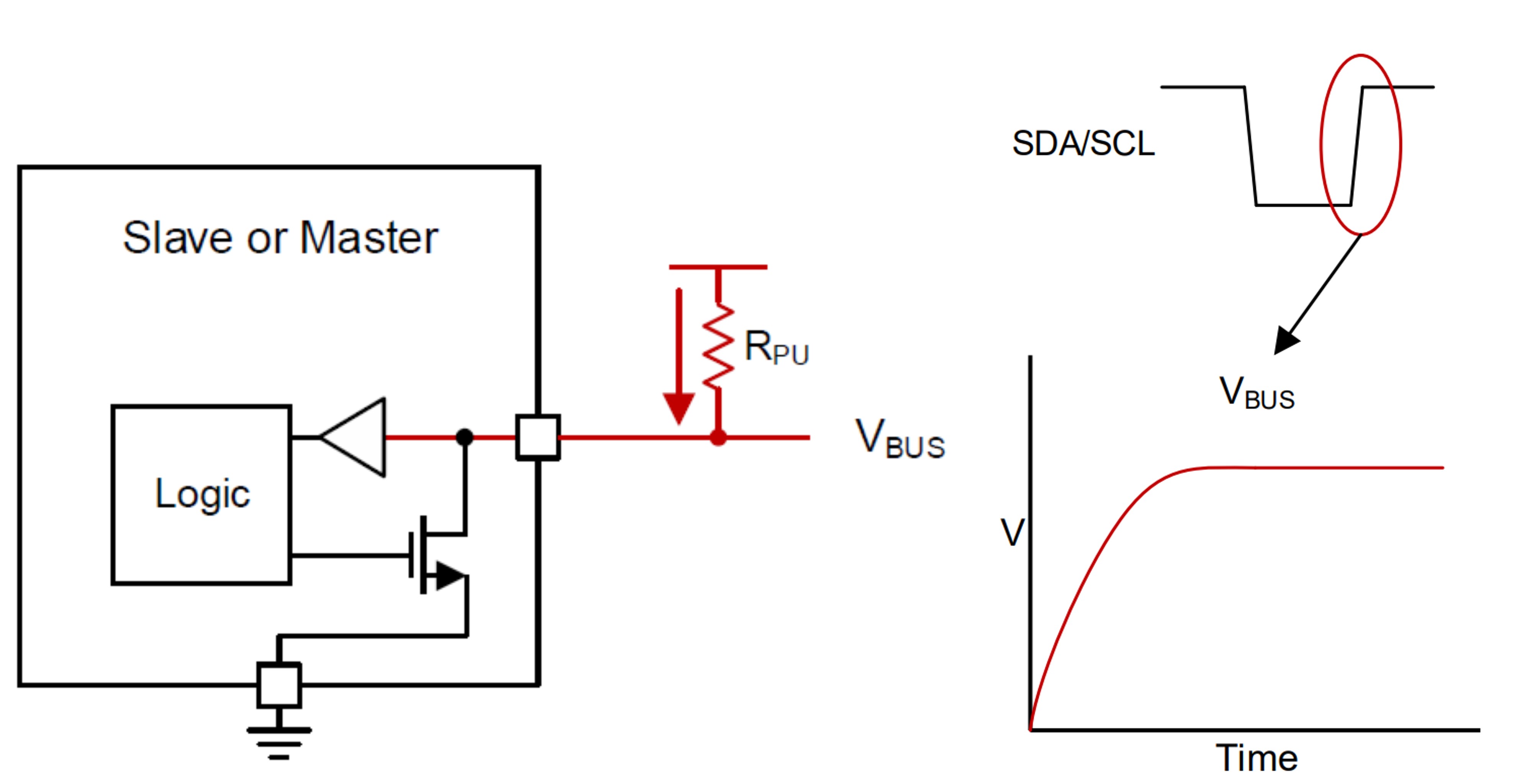

Basic Internal Structure of SDA/SCL Line

I2C uses an open-drain/open-collector with an input buffer on the same line, which allows a single data line to be used for bidirectional data flow.

I2C는 동일한 라인에 입력 버퍼가 있는 오픈 드레인/오픈 컬렉터를 사용하므로 양방향 데이터 흐름에 단일 데이터 라인을 사용할 수 있습니다.

FET On, VBUS Low, Open-Drain Pulling Low

FET off, VBUS high, Open-Drain Releasing Bus

I2C Basic Design

Multiple Master & Slave

I2C 통신에서 공통의 SCL/SDA 라인을 이용해 하나의 Master로 여러 개의 Slave를 제어할 수 있는 이유는 Master에서 Slave의 주소 (Address) 값으로 각각의 모듈을 구분하기 때문입니다. Slave의 주소 값은 일반적으로 7 bits 값을 가지기 때문에 이론상 하나의 Master와 128 개의 Slave를 동시에 연결할 수 있습니다.

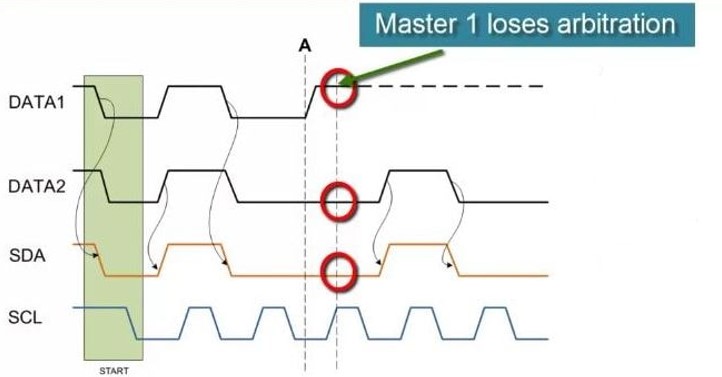

Arbitration in I2C Bus

For Example,

Suppose two masters in the I2C bus try to communicate with a slave simultaneously and assert a start condition on the bus. The SCL clock of the I2C bus would be already synchronized by the wired and logic.

만약에, 두개의 마스터가 동시에 Start condition으로 통신을 시도했다면, I2C는 오픈드레인 구조로 하나의 라인이라도 Low이면 SDA는 Low이므로 늦게까지 Low인 상태를 유지하는 Data를 보내는 모듈과 통신합니다.

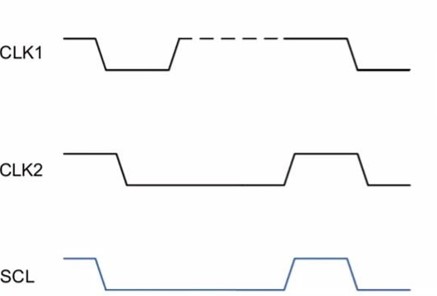

Clock synchronization in I2C

I2C is synchronous communication, in which a clock is always generated by the master and this clock is shared by both master and slave.

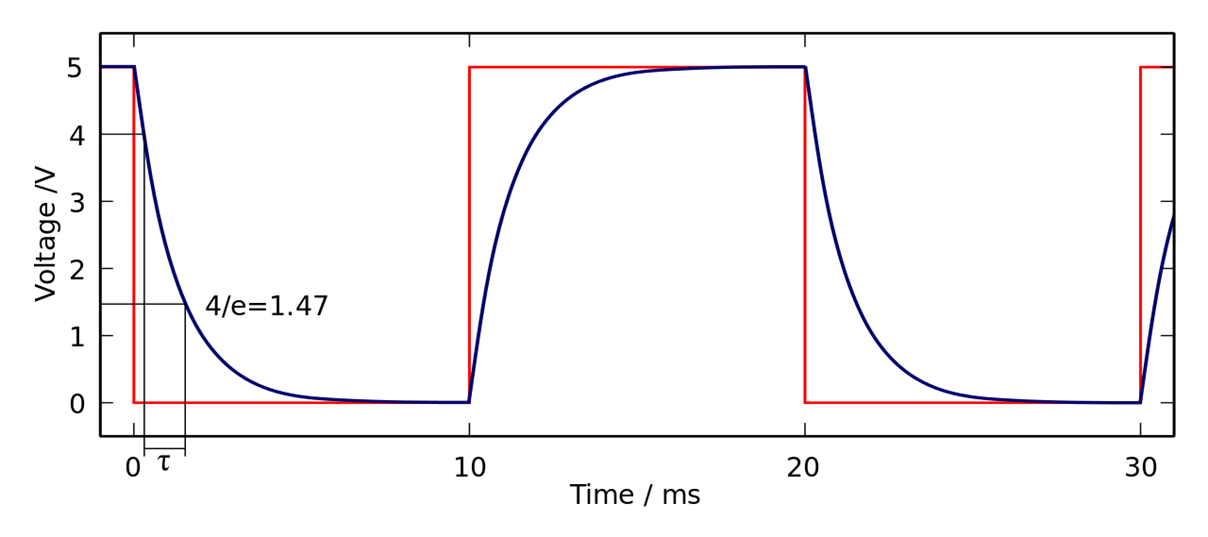

FET 동작에 따른 출력 신호 파형

Pull-up 실제 I2C 파형

풀업 저항 값 R 과 여러 장치들이 연결 되면서 발생하는 캐패시턴스 값에 의해서 Rising, Falling 시간이 느리다. (고속 동작에 불리한 구조)

2023.06.21 - [Knowledge] - I2C? (2)

I2C? (2)

2023.06.21 - [Protocol] - I2C? (1) I2C? (1) I2C is "Inter-Integrated Circuit" Interface SCL : Serial Clock (Output from master) SDA : Serial DATA (Data In & Out port) I2C 프로토콜은 하나의 데이터 라인 (SDA)과 하나의 클럭 라인 (SCL)을

vir-us.tistory.com

2023.06.21 - [Knowledge] - I2C? (3)

I2C? (3)

2023.06.21 - [Protocol] - I2C? (1) I2C? (1) I2C is "Inter-Integrated Circuit" Interface SCL : Serial Clock (Output from master) SDA : Serial DATA (Data In & Out port) I2C 프로토콜은 하나의 데이터 라인 (SDA)과 하나의 클럭 라인 (SCL)을

vir-us.tistory.com

'Knowledge > Protocol' 카테고리의 다른 글

| [Ethernet] Auto-Negotiation이란? (0) | 2023.07.04 |

|---|---|

| [AXI] Low Power Interface (ENG) (0) | 2023.06.30 |

| I2C? (3) (0) | 2023.06.21 |

| I2C? (2) (0) | 2023.06.21 |

| [Ethernet] Packet formet (0) | 2023.06.21 |