2023.06.21 - [Knowledge] - I2C? (1)

I2C? (1)

I2C is "Inter-Integrated Circuit" Interface SCL : Serial Clock (Output from master) SDA : Serial DATA (Data In & Out port) I2C 프로토콜은 하나의 데이터 라인 (SDA)과 하나의 클럭 라인 (SCL)을 이용하는 동기식 (synchronous) 시리

vir-us.tistory.com

2023.06.21 - [Knowledge] - I2C? (2)

I2C? (2)

2023.06.21 - [Protocol] - I2C? (1) I2C? (1) I2C is "Inter-Integrated Circuit" Interface SCL : Serial Clock (Output from master) SDA : Serial DATA (Data In & Out port) I2C 프로토콜은 하나의 데이터 라인 (SDA)과 하나의 클럭 라인 (SCL)을

vir-us.tistory.com

목차

I2C Basic Operation

Wirte

Start 조건 이후, Master는 통신하고자 하는 Slave의 주소 값 7 bits와 R/W 값 1 bit를 전송한다. R/W 값은 Read(1)와 Write(0) 동작을 구분하는 비트입니다.

만약, 입력한 Slave 주소에 대응되는 모듈이 있는 경우 해당 Slave는 Master로 ACK 신호를 전달합니다. ACK 신호를 전달 받은 Master는 Write 하고자 하는 Slave 내부의 데이터 영역을 선택하기 위해 8 bits 크기의 레지스터 정보를 전송합니다. 이 과정은 Write 가능한 레지스터에 대해 수행되어야하며, 문제가 없을 경우 Slave는 다시 ACK 신호를 전달합니다. 레지스터 선택을 완료한 이후, Master는 해당 레지스터에 원하는 데이터를 BYTE 단위로 전송하며, 하나의 BYTE 전송이 끝날 때마다 Slave로부터 ACK 신호를 수신합니다.

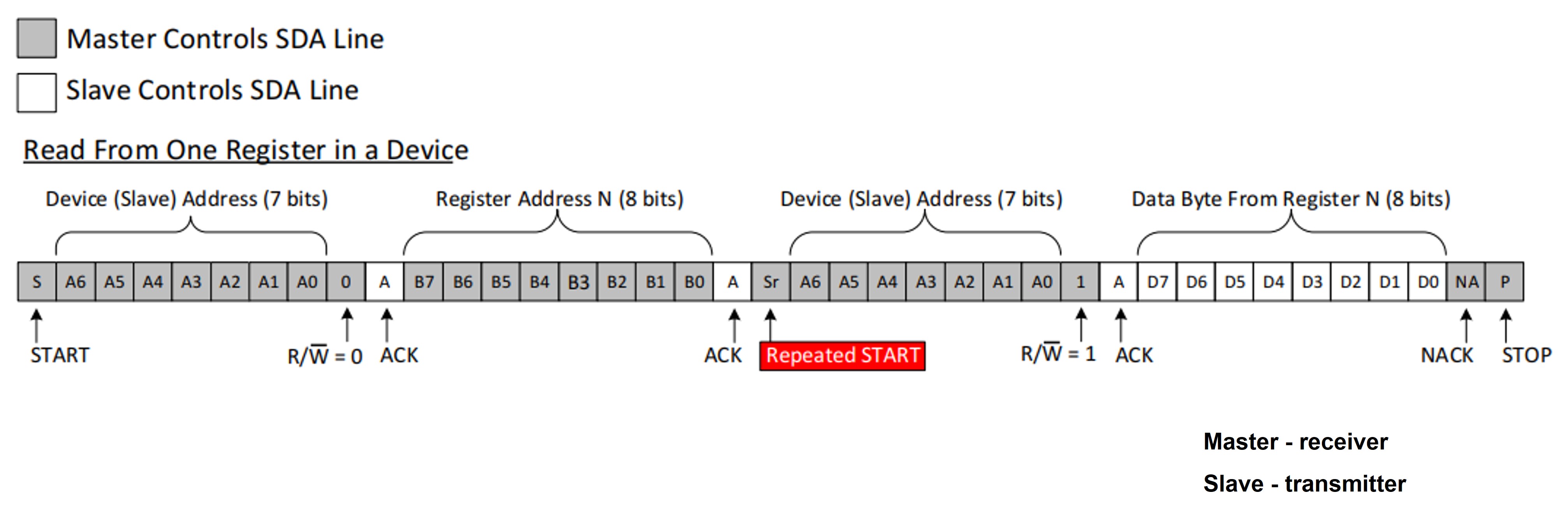

Read

Master에서는 Read 동작을 수행하는 경우에도, Slave에게 어떤 레지스터 값을 읽어올지 알려줘야 하기 때문에 Write 동작을 먼저 수행합니다. 그렇기 때문에, 처음에 Slave 주소를 전송하고 레지스터를 선택하는 시점까지는 Read/Write 시퀀스가 동일한 것을 볼 수 있습니다.

레지스터를 선택 후, Read 시퀀스에서는 Master가 Start 신호를 다시 전송하며(Repeated START), Slave 주소와 함께 R/W 비트 값을 1로 전송하면, Slave에서는 이전에 선택된 레지스터의 값을 Master로 전송해줍니다.

I2C Special Operation

Repeated Start Conditions

Sometimes, it is important that a controller be allowed to exchange several messages in one go, without allowing other controllers on the bus to interfere. For this reason, the repeated start condition has been defined. To perform a repeated start, SDA is allowed to go high while SCL is low, SCL is allowed to go high, and then SDA is brought low again while SCL is high. Because there was no stop condition on the bus, the previous communication wasn't truly completed, and the current controller maintains control of the bus.

At this point, the next message can begin transmission. The syntax of this new message is the same as any other message--an address frame followed by data frames. Any number of repeated starts is allowed, and the controller will maintain control of the bus until it issues a stop condition.

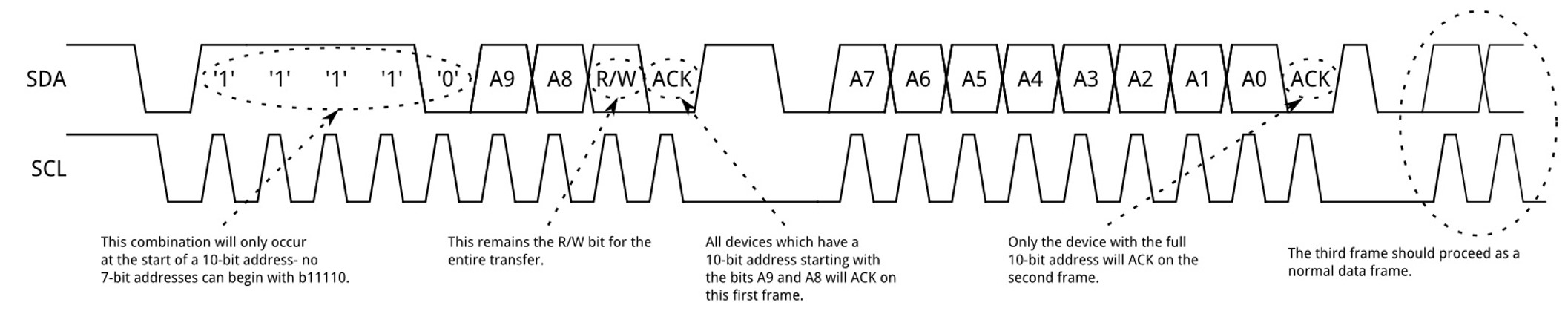

10-bit Addresses

In a 10-bit addressing system, two frames are required to transmit the peripheral address. The first frame will consist of the code 8’b11110xyz, where 'x' is the MSB of the peripheral address, ‘y’ is bit 8 of the peripheral address, and ‘z’ is the read/write bit as described above. The first frame's ACK bit will be asserted by all peripherals which match the first two bits of the address. As with a normal 7-bit transfer, another transfer begins immediately, and this transfer contains bits 7:0 of the address. At this point, the addressed peripheral should respond with an ACK bit. If it doesn't, the failure mode is the same as a 7-bit system. Note that 10-bit address devices can coexist with 7-bit address devices, since the leading '11110' part of the address is not a part of any valid 7-bit addresses.

Clock Stretching

Communication in the I2C bus can be paused by the clock stretching to hold the SCL line low and it cannot continue until the SCL line is released high again.

In I2C, the slave able to receive the data at a fast rate but sometimes the slave takes more time in the processing of received data. In that situation, slave pulls the SCL line low to pause the communication and after the processing of the received bytes, it again released the SCL line high to resume the communication. The clock stretching is how slave drive the SCL line, but it is the fact, most of the slave does not drive the SCL line.

Note: In the I2c communication protocol, most of the I2C slave devices do not use the clock stretching feature, but every master should support the clock stretching.

'Knowledge > Protocol' 카테고리의 다른 글

| [Ethernet] Auto-Negotiation이란? (0) | 2023.07.04 |

|---|---|

| [AXI] Low Power Interface (ENG) (0) | 2023.06.30 |

| I2C? (2) (0) | 2023.06.21 |

| I2C? (1) (0) | 2023.06.21 |

| [Ethernet] Packet formet (0) | 2023.06.21 |